dsrinivasrao

Member level 1

hi all,

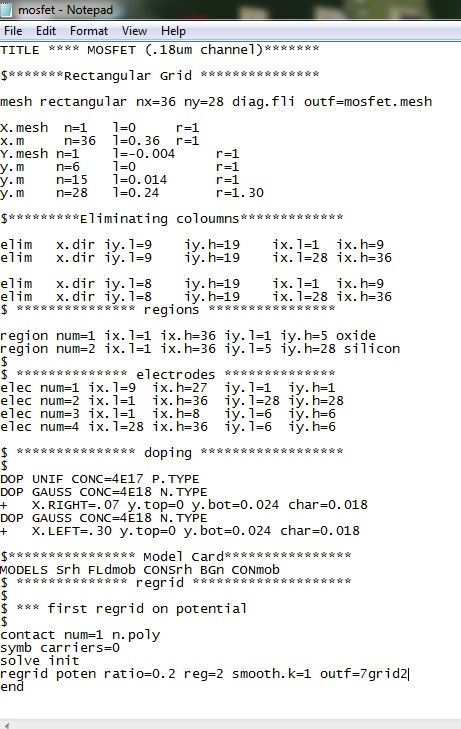

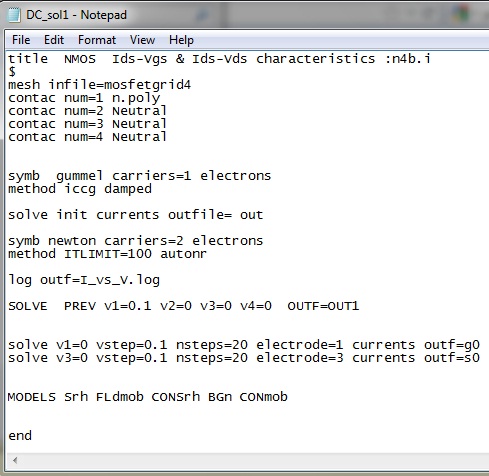

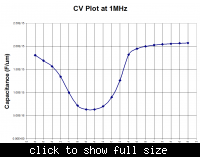

I am Using PISCES POSTMINI TOOL for the device simulation ,Can somebody plz tell me how to plot different curves for same or different variable on the same plot???...Plz help me...

I am Using PISCES POSTMINI TOOL for the device simulation ,Can somebody plz tell me how to plot different curves for same or different variable on the same plot???...Plz help me...